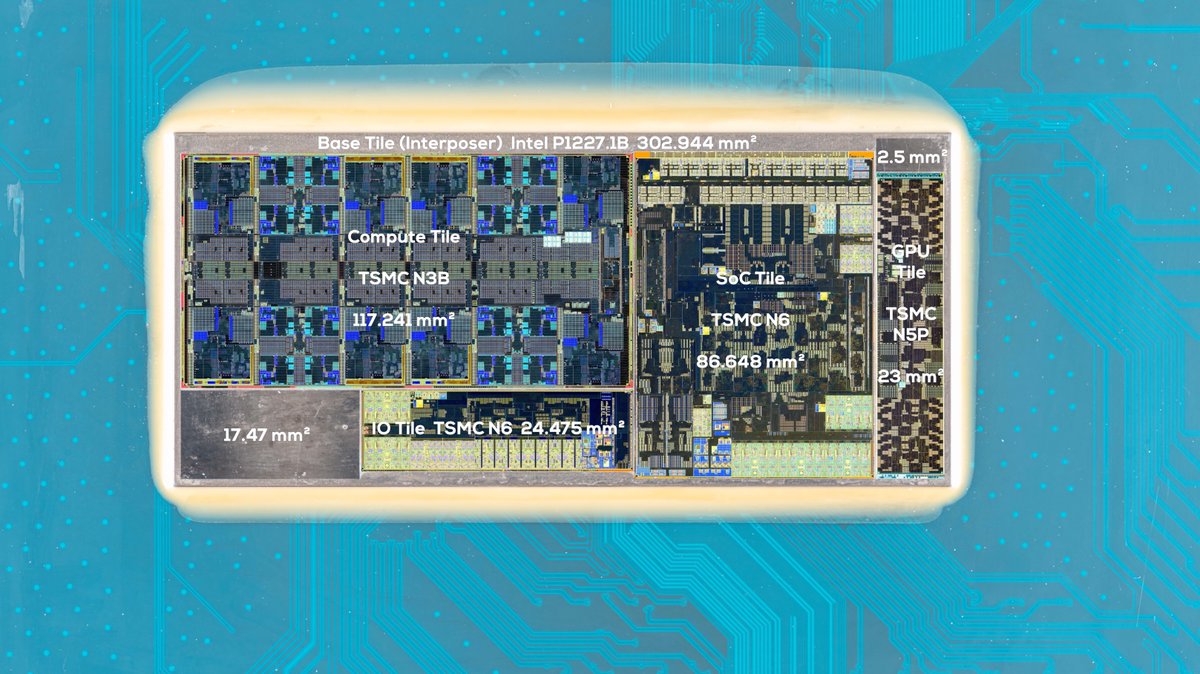

Die shots shared by Andreas Schilling on X expose the Core Ultra 200S silicon in excruciating detail. You get the compute tile perched on the upper left, an IO tile below it, and the SoC and GPU tiles crammed on the right. Chipzilla’s also wedged in two filler dies for structural stability, suggesting even the layout has to be held together with scaffolding.

As Tom's Hardware points out: " Moving to a chiplet approach will afford Intel more ways to optimize its architectures down the road, in a more efficient manner. Each tile can be developed independently of others and built with different nodes to improve yields, optimise development, and reduce production costs."

The compute tile is fabbed on TSMC’s bleeding-edge N3B node with a 117.241 mm² footprint. The IO and SoC tiles are built on TSMC’s older N6 process, measuring 24.475 mm² and 86.648 mm² respectively. Holding it all together is a base tile done on Chipzilla’s own crusty 22nm FinFET process, one of the few parts it didn't outsource.

This is the first time Chipzilla has used only third-party fabs for every active tile. Probably because its own foundries are still paddling in the shallow end of process technology.

The IO tile has Thunderbolt 4 controllers, PCIe PHYs, and display outputs. The SoC tile handles media engines, more PCIe, and DDR5 memory controllers. GPU duties fall to four Xe cores and a slice of Arc Alchemist.

Arrow Lake’s new core layout shows some brains in thermal planning. Instead of lumping all the E-cores together, Chipzilla scattered them between the P-cores to help spread the heat out. Eight P-cores each get 3MB of L3 cache and flank the edges and centre. Four E-core clusters sit between them and pull 3MB of L2 cache per cluster. For the first time, the E-cores also get a slice of L3 shared with the P-cores.

Nice layout. Shame about the results.

Despite all the tile-toting and silicon artistry, Arrow Lake’s gaming performance gets wrecked by AMD’s Ryzen 9800X3D and even Chipzilla’s 14900K. The big drag is latency from the interconnect that links the tiles. Firmware patches are in the works but that won’t change the basic plumbing. The chiplet approach might eventually pay off. You can build each tile separately on the best node for the job, improving yields and cutting costs. But right now, Arrow Lake is a looker with lag.